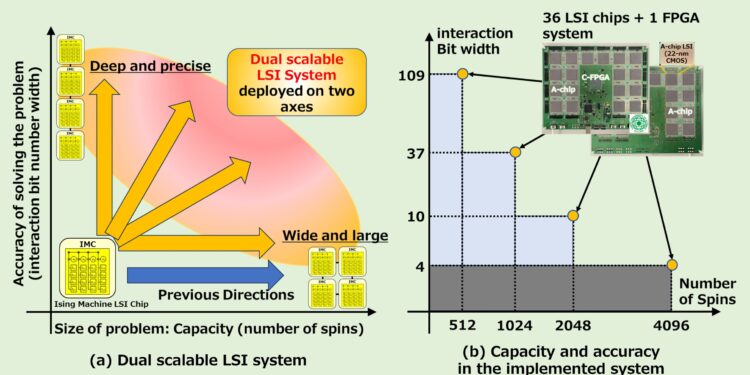

The proposed system allows simultaneous expansion of the number of spins and interaction bit width using several identical LSI chips, resulting in more precise and effective solutions for combinatory optimization problems. Credit: Takayuki Kawahara of the University of Sciences of Tokyo, Japan

Combinatory optimization problems (COP) occur in various fields such as quarter planning, traffic routing and drug development. However, they are difficult to resolve using traditional computers in a practical time.

Alternatively, the receipt processors (AP), which are specialized equipment to resolve COPs, have drawn significant attention. They are based on the Ising model, in which COP variables are presented in the form of magnetic spins and constraints as interactions between spins. The solutions are obtained by finding the state of spin which minimizes the energy of the system.

There are two types of Ising models, the low -guilty coupling model and the fully coupled model. Lighting models offer great scalability by allowing more tricks, but require that the cops are transformed to adapt to the model. The fully coupled models, on the other hand, allow any cop to be mapped directly without transformation, which makes them highly desirable.

However, they are limited in capacity (number of spins) and in precision (width of the interaction bit). Although previous studies have implemented models entirely in isss using an evolutionary structure which can increase the capacity using integrated circuits specific to the application (ASIC), their interaction bits width is fixed, which makes certain cops difficult to solve.

In a new study, a research team from Japan, led by Professor Takayuki Kawahara of the Department of Electric Engineering at the University of Sciences of Tokyo, has developed an innovative evolving (DSAPS) Grave Treatment system which can simultaneously both capacity and precision using the same evolutionary structure. Their study appears in the journal IEEE access and was presented at the 2024 international conference on microelectronics.

DSAPS performs the double scalability by manipulating the ∆E blocks, responsible for calculating the energy of the system, using two structures. That is to say, the conventional high capacity structure and a new high-precision structure. Each block ∆E is equivalent to an integrated (LSI) chip on a large -scale map based on CMOS and includes the interaction matrix and spins.

The high-capacity structure divides each block ∆E into smaller sub-blocks which are calculated separately then added by a control block on the AP card. This increases the number of spins by simply subdivided the ∆E block in addition to sub-blocks.

The high -precision structure makes it possible to calculate several ∆E blocks, with the same numbers and spin interactions, to be calculated at different water levels. The control block then combines their calculations by making bits changes, which leads to a higher overall interaction bits width. For example, a system with four ∆E blocks operating at different bits levels with a single control block can manage the width of the original interaction bit four times.

“DSAPS is a revolutionary system which allows simultaneous expansion of the number of spins and interaction bit width by controlling several identical LSI chips with a program of programmable door control in field,” explains Professor Kawahara. “In addition, this system can be used for Ising models with little coupled and fully coupled coupling.”

To demonstrate the practical aspect of the system, the researchers implemented two DSAPS configurations on a CMOS-AP card using spin threads: one with 2,048 laps, with 10-bit and four thread interactions, and another with 1024 spins, 37-bit interactions and two threads. This is a considerable improvement compared to ASICs, which generally have interaction bits of only 4 to 8 bits.

Validation tests on maximum cutting problems have shown that the two DSAPs have reached a precision of more than 99% compared to the best known theoretical results. However, in the 0-1 backpack problem, DSAPs with 10-bit interaction showed a large average difference of 99%, while the 37-bit configuration showed a much lower average difference of only 0.73%, near that observed in emulation based on the processor. This highlights the importance of selecting a DSAPS configuration that aligns with the characteristics of the target COP.

“This system will prove to be crucial to developing evolutionary APPs to resolve complex world cops,” notes Professor Kawahara. “Our department has promoted research on the implementation of the ISING MACHINES entirely coupled for 10 years. From 2025, this system will be integrated as one of the student experiences for all third year students, improving education in the design of semiconductors.”

Overall, this study marks a significant step for the development of high precision and fully coupled Ising Ising machines, with promising applications in various fields.

More information:

Dong Cui et al, double scalable removal treatment system which simultaneously evolves the number of spins and interaction IEEE access (2025). DOI: 10.1109 / Access.2025.3553542

Provided by the University of Sciences of Tokyo

Quote: Double evolutionary receipt processors overcomes the capacity and the precision limits (2025, April 28) recovered on April 28, 2025 from

This document is subject to copyright. In addition to any fair program for private or research purposes, no part can be reproduced without written authorization. The content is provided only for information purposes.